出國報告(出國類別:出國短期研究)

獵能感應器應用服務、系統軟體與處 理器之研究

服務機關:資訊工程系

姓名職稱:曹孝櫟副教授

派赴國家:瑞士蘇黎世聯邦理工大學

出國期間:102/07/01-08/15

報告日期:102/12/31

## 摘要

本計畫針對使用環境能源供電之穿戴式感應器裝置所應具備的環境包含應用程式(Applications)、程式語言(Programming language)、程式撰寫模型(Programming model)、編譯器和程式發展工具(Compiler and development tools)、執行階段支援系統(Run-time support)與作業系統(Operating system)、低耗電低電壓感測器處理器等做一深入的探討與研究,並思考以程式語言之改進與擴充、編譯器之支援,作業系統與動態執行階段之耗電感知與電源管理能力,以及底層硬體之支援與配合,已達到資通訊系統高效能低耗電之目標。本次出國目的除了延續並完成與國際百大合作學校瑞士蘇黎世聯邦理工大學(ETH Zurich)之合作技術開發與研究外,同時也完成與瑞士蘇黎世聯邦理工大學(ETH Zurich)兩校交換學生合約之簽訂工作。

# 目次

| <u> </u> | 目的        | 4 |

|----------|-----------|---|

| 二、       | <b>過程</b> | 4 |

| 三、       | \         | 3 |

### 一、目的

本人參與國際百大合作計畫"獵能感應器應用服務、系統軟體與處理器之研究"與瑞士蘇黎世聯邦理工大學(ETH Zurich)合作進行使用環境能源供電之穿戴式感應器裝置之程式語言、程式撰寫模型、編譯器和程式發展工具、執行階段支援系統與作業系統、低耗電低電壓感測器處理器等之研究。在此之前已透過國科會申請國內研究學者短期訪問一年(2012/07/01-2013/06/30),為接續完成研究工作並完成與瑞士蘇黎世聯邦理工大學(ETH Zurich)兩校交換學生合約之簽訂工作,因此申請本次延長訪問計畫。

#### 二、過程

瑞士蘇黎世聯邦理工大學(ETH Zurich)為歐洲最著名之大學之一(世界排名第 12 名(THE-QS World University Rankings 2013 排名)/歐洲大陸排名第 1 名 (THE-QS World University Rankings 2013 排名)/資訊工程世界排名第 26 名(上海交大 2013 排名)),見圖一,而合作之主要研究單位為資訊工程學院前院長 Prof. Jurg Gutknecht 所領導之 Native Systems Group 團隊以及 Institute for Computer Systems,見圖二。Native Systems Group 為發展電腦程式語言 PASCAL 之發源地,目前仍專注於電腦系統包含處理器、系統軟體、程式語言之設計與研究。Native Systems Group 之專長在於超過 20 年,長時間投入程式語言、編譯器、作業系統、與處理器之設計與發展,擁有極為穩定與成熟之自主性程式語言、編譯器、作業系統、與處理器之設計與實作。

本人於 2012/07/02 報到後,立即被安排至 Institute for Computer Systems 系館之個人研究室,如圖三。本此延長訪問期間,則繼續使用該研究室開始研究討論工作。

圖一 瑞士蘇黎世聯邦理工大學(ETH Zurich)主校區建築

圖二 蘇黎世聯邦理工大學接待教授 Prof. Jurg Gutknecht

圖三 蘇黎世聯邦理工大學 Institute for Computer Systems 系館與本人之個人研究室

本次延長短期研究研究主題之一是延續前一年度和蘇黎世聯邦理工大學的 合作,從上層應用為出發,以獵能感應器為例,探討耗電感知計算的核心問題。

未來的穿戴式感應器裝置除了使用電池運作之外,將考慮環境能源供電,例如太陽能,環境熱能,環境風能,使用者行動所產生的動能等。然而這樣不穩定的供電行為將對感應器裝置,由其是軟體的開發與設計,造成相當大的衝擊與挑戰。在這個計畫中,我們針對使用環境能源供電的穿戴式感應器裝置所應具備的環境包含應用程式(Applications)、系統軟體如通訊協定(Wireless Communication Protocol)、程式語言(Programming language)、程式撰寫模型(Programming model)、編譯器和程式發展工具(Compiler and development tools)、執行階段支援系統(Run-time support)與作業系統(Operating system)、低耗電低電壓感測器處理器等做一深入的探討與研究。並提出適合穿戴式感應器裝置上的應用演算法、通訊協定、程式程式語言、執行階段支援系統、作業系統(Operating system)、低耗電低電壓感測器處理器,以方便程式發展者快速發展穿戴式感應器裝置上的應用服務而無須擔憂不穩定的環境能源因素。

耗電問題一直是穿戴式感應器裝置最重要的問題之一,傳統的穿戴式感應器裝置以電池運作,一段時間就必須充電,在使用上造成很大的麻煩。搭配環境能源如太陽能,環境熱能,環境風能,使用者行動所產生的動能等來驅動穿戴式感應器裝置是一個新興的研究課題,然而環境能源來源可以不穩定也不規律,例如太陽的入射角和使用者運動強度,都會造成產生電壓與電流大小的不同,此外環境能源產生技術也可以透過調整供電壓與供電量來延長能源使用時間,因此在這種供電特性下,穿戴式感應器裝置的微處理器必須考慮支援多種運作模式(包含速度、功能、消耗電壓與所需時脈),穿戴式感應器裝置也必須考慮現有的工作量與能源狀況來調整處理器速度以達到最佳的匹配。從另一個角度來看,軟體必須在處理器有足夠供電的狀況下才能運作,排程器必須考慮能源是否足夠執行該工作、有多少工作與功能需要被開啟等。在電源不足的情況下,排程器應該中斷程式的執行,進入極省電的狀態保持階段,待環境能源出現時,再度啟動程式繼續執行,不適當的排程或是不當順序的執行,可能會造成工作未完全執行結束必須重新執行,或是處理器被迫中斷,資料遺失程序必須重新執行的現象,造成額外的能源耗損與浪費。

在硬體方面,為了達成低功率 SoC 處理器設計,一般來說,DVS (dynamic voltage scaling), 低電壓, and Sleep-mode 的支援為基本不可或缺要項。下表整理目前業界低功率(low-power)/低電壓(low-voltage) SoC 處理器比較,主要為其公司的技術帶來的效能和功率消耗之間的調整。除了功率消耗最大的的元件-processor 之外,記憶體所耗費的功率也相當可觀。因此記憶體功率最佳化亦為一重要課題,改善此部分往往有著最大的功率消耗。例如 Intel Atom 與 VIA Nano為筆記型電腦提供更低的功率消耗,相較於傳統動輒上 100W,其功率消耗僅有0.6~25W (sub-watt level),其對於筆記型電腦的續航力影響甚劇,大大的改善傳統使用者對於筆記型電腦待機時間不足的觀感。其中 Intel Atom 支援0.7~1.2V/0.8~2.0GHz 的 DVS 以及 0.3V sleep-mode,另外在記憶體(Registerfile, SRAM), Clock-tree, and Ground-breaking power management ... 等大量功率消耗原件進行最佳化。VIA Nano著重於 performance/power/ temperature monitor and management,以動態調整其所定義之 P-state voltage 達到最佳的電能管理,另外在其 standby mode 的功率消耗僅有 100~500mW。

基於上述描述,此次短期研究成果以具備耗能感知之程式語言擴充為主:目前的程式語言無法表達程式撰寫者對程式效率和程式耗電的需求。因此編譯器無法從中得知使用者對於該程式或該程式區段所期盼的效能表現或耗能表現。在具備耗能感知之軟體環境中,效能表現和耗能表現常常相互影響,本計畫擴充程式語言,讓程式發展者可以輕易表達程式或程式區段的效能和耗能表現是重要的研究課題。例如在一個穿戴式感應器裝置進行心電圖(ECG)的應用程式撰寫,穿戴式感應器裝置每秒進行 500 次心電圖取樣,若穿戴式感應器裝置無法在 2ms 內完成處理,則應用程式將產生問題,然後在程式語言中若能加入描述,明確表達在 2ms 內完成處理的原則下,盡量降低耗電,這樣的程式語言設計將可以協助程式發展者描述其對效能和耗能的處理原則,在此原則下,軟體工具如編譯器則可添加相關電源管理模組,以達成效能之耗電最小化作為程式產生標準。另一方面,以心電圖(ECG)應用為例,其需求規格可能希望一個 200mAh/1V 的電池可以支援 200 小時,使用者若能透過程式語言表達在此一耗電需求標準下,希望盡

可能提升效能,一樣可以達成耗能需求且效能最佳化的設計。具備耗能感知之執行支援系統擴充:當能源不足時,應用程式可以關閉部分功能、降低計算解析度、降低效能需求、延後工作執行等以調節耗電。在此時執行支援系統的即時資訊提供以及搭配的程式語言和程式工具讓使用者可以描述其需要以及相對應的反應程序是非常重要的功能。以心電圖(ECG)應用為例,當環境能源不足時,可以減少取樣速率,或延後取樣的處理直到電源穩定供應為止。

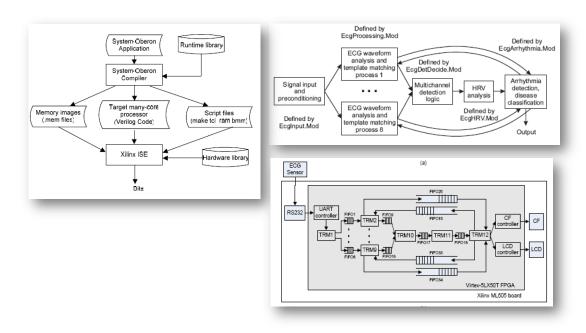

Gutknecht 教授和他的研究小組提出的語言稱為 System Oberon,其主要設計理念是方便系統設計師開發包括嵌入式系統的硬體和軟體。系統設計者首先描述他們的系統,此後 System Oberon 系統編譯器生成特定的多核心嵌入式硬體,同時生成高效率的應用程式,以多線程的方式在多核處理器上運行。System Oberon編譯系統所產生的硬體描述和硬體配置檔,可以進一步透過硬體合成器(synthesis tool)例如 Xilinx ISE,產生一個 FPGA 的硬件。圖四顯示了使用 System Oberon和基於 FPGA 的嵌入式多核系統的設計流程加以實做心電圖(Electrocardiography, ECG)系統。

圖四 System Oberon 及其 FPGA 為基礎之嵌入式多核系統之設計流程 (Figure source: Lisa Liu and Oleksii Morozov, "A Process-Oriented Streaming System Design Paradigm for FPGA," submitted for publication).

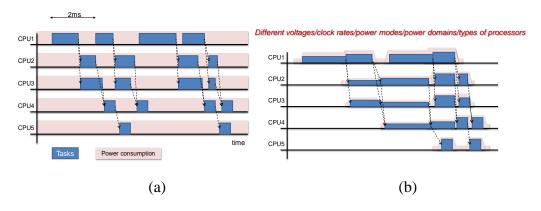

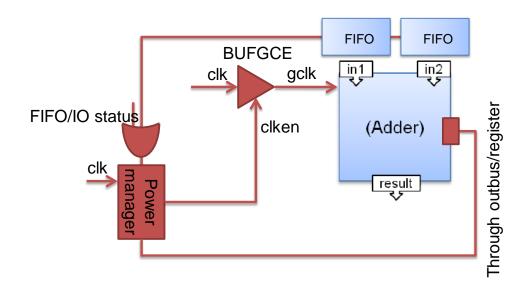

功率消耗是嵌入式多核系統一個重要的問題。使用 System Oberon 的好處之一是因為編譯器能產生高效的硬體和其執行的應用軟體。然而,過去的設計多半以提升效能為考慮,目前的工具包含 System Oberon 在內皆無法生成電源管理功能的硬體。在多核系統中,CPU 核心平行執行程式,有時 CPU 間互相溝通協調的工作和傳遞資料。如果沒有精確管理每顆 CPU 核心、CPU 核心之間的通信、CPU 核心之工作速度和 CPU 核心電壓,CPU 核心將消耗額外的電源。圖五(a)顯示如果所有的 CPU 核心上都使用最大和相同的速度運行,該系統會浪費最多電力。因此,在這次研究訪問期間,我與 Gutknecht 教授和他的研究小組討論以修改 System Oberon 的設計,使其在提高速度的同時可以降低耗電。設計的概念是增強 System Oberon 讓系統設計師在開發自己的系統時可以指定功耗的要求(energy requirement)。編譯器可依照系統設計師的要求生成必要的硬體,以優化嵌入式多核系統之耗能效率為主,生成具有電源管理功能的硬體,同時生成的軟體也可以利用這些具備特殊功能的電源管理功能硬體,在協同工作下盡量減少系統的功耗。圖五(b)顯示新的軟硬體生成工具基於功耗要求所生成的軟硬體。

圖五 透過耗電感知之硬體與軟體生成器產生低耗電之嵌入式系統

#### Low power attributes and performance/power requirements

```

Adder= ACTOR (in1,in2: STREAM {IN} OF INTEGER; result: STREAM {OUT} OF INTEGER)

VAR summand1, summand2: INTEGER;

BEGIN

LOOP

RECEIVE(in1, summand1);

RECEIVE(in2, summand2);

SEND(result, summand1 + summand2)

END

END Adder;

```

圖六 耗電感知之硬體擴充設計

圖六和圖七顯示出我們所提出的基於耗電感知之硬體與軟體擴充設計。圖六顯示系統設計者可以以 System Oberon 語言定義系統以效能優化為主或以耗能優化為主之需求。系統設計師提供的需求後,System Oberon 編譯器生成所需的低功耗硬件和額外的電源管理硬體到 FPGA 平臺。例如,在圖六中,系統設計人員在系統描述中添加了低功耗的屬性,編譯器會自動合成電源管理硬體組件到到原有硬體設計中。之後系統設計師便能夠在開發耗電感知之應用程式時使用的電源管理功能。圖七提供了一個設計案例,系統設計人員可以使用如睡眠和閒置等的電源管理功能。此外,忙碌等待(busy waiting)功能被自動轉換到睡眠喚醒(sleep-wakeup)的版本,可大幅消耗功耗。

```

BEGIN

Low power attributes and performance/power requirements

LOOP

y := a+b;

RS232.SendInteger(y);

RS232.SendEnd;

SYSTEM.PUT(ledAdr, y);

IDI F

RECEIVE(in, a);

END;

END TestTRM2.

Low power attributes and performance/power requirements

BEGIN

resettimer(PMConfig.7)

LOOP

y := a+b;

REPEAT UNTIL checkreceive(in, a) Or timerexpire()

RS232.SendInteger(y);

IF timerexpire() THEN

RS232.SendEnd;

stoptimer()

SYSTEM.PUT(ledAdr, y);

Idle

RECEIVE(in, a, PMConfig);

END

END;

RECEIVE(in, a);

END TestTRM2.

```

圖七 耗電感知之程式語言與編譯器擴充設計

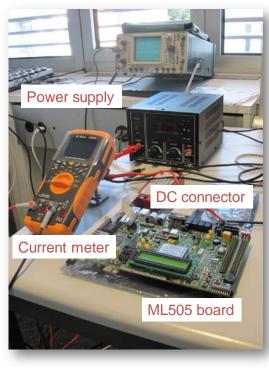

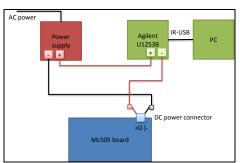

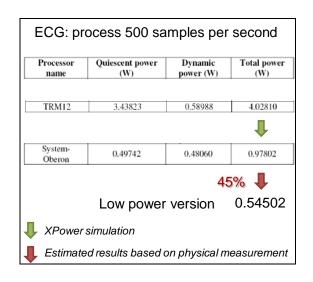

在此研究中,我們不僅增強了系統描述語言和系統編譯器的功能,使其支援 耗電感知的能力,此外修改了支援 System Oberon 之 RISC 計算機處理器稱之為 微暫存器機器(Tiny Register Machine, TRM)之硬體設計,擴充其多項電源管理的 功能。我們使用心電圖應用系統驗證我們的設計,同時比較前後在能源消耗方面 的表現,我們建立了功耗量測平臺如圖八所示。我們在此平臺上進行實作、測量 和評估,圖九顯示實驗結果。與一般通用多核嵌入式系統相比,我們的耗電感知 可以進一步降低 45%功耗。

圖八 耗能量測評估平臺

圖九 耗能評估結果

系統層級的設計環境對嵌入式系統的開發來說是非常重要的。耗電感知計算 之編譯器與處理器設計是建構高效率低耗電硬體和軟體的重要基礎研究。本次國 外短期研究與蘇黎世聯邦理工大學合作完成了耗電感知計算之軟硬體開發環 境,初步實驗結果證實在不影響效能的原則下雛型心電圖系統可以獲得 45%功 耗改善,除部分研究成果以合作發表論文外。其他相關研究正積極整裡投稿中。

### 三、心得及建議

此次出國短期研究主要延續國科會所補助之國內研究學者短期訪問,為接續完成研究工作,同時完成與瑞士蘇黎世聯邦理工大學(ETH Zurich)兩校交換學生合約之簽訂工作。除研究成果正積極整裡投稿外,對蘇黎世聯邦理工大學之教學研究環境有下列心得。

培養熱情研究態度並嚴格要求:透過各種方式培養學生的興趣並讓他們學習最熱愛的主題,花相當多的心思激發學生研究與學習熱情,協助學生探索自己的興趣和天份。但此外嚴格要求學生,必修課多半有一半以上淘汰率。同一門必修課修兩次沒過就退學,對學生要求極為嚴格,學校以培育高素質人才為唯一目標。

重視系統技術與實作:蘇黎世聯邦理工大學規定一周三小時的課程裡必須有 1/3 的時間用來進行動手實驗。學生了解任何一個課程, "動手"是基本的訓練和 要求。"動手"在工程教育裡的重要性,融入在這裡的老師、學生的心理。加強動 手訓練可提升工程訓練與教育品質。